# **Active Silicon**

# SNAPPER-PCI-8/24

# MONOCHROME • RGB • YCbCr • VIDEO DIGITIZER

- High quality analogue video acquisition board with square pixel sampling for CCIR, EIA (RS-170) standards, and non-standard video formats.

- Supports configurable RS-422 or TTL control, pixel clock and external trigger.

- Software programmable on-board sync generator.

- 8 bit Look Up Tables (LUTs).

- Software programmable black, white and clamp levels.

- On-board frame store with high speed readout, including PCI bus interface supporting 132 Mbytes/sec burst transfers. Support for master and slave operation.

- Hardware Region of Interest (ROI) and sub-sampling.

- On-board Data Mapper for hardware pixel mappings.

- Software Development Kit (SDK) for rapid integration.

## **OVERVIEW**

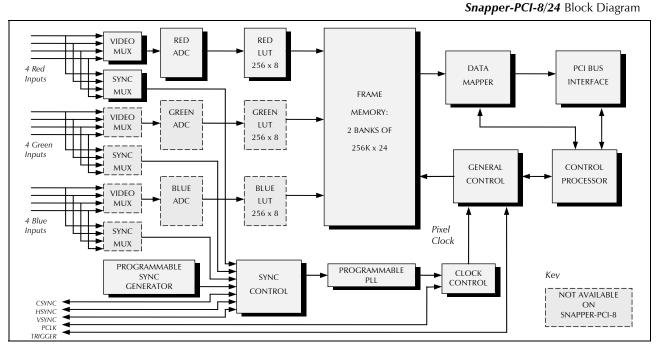

**Snapper-PCI-8/24** is high speed PCI board for the acquisition of standard CCIR or EIA/RS-170 video standards as well as slow scan and line scan cameras. The board is available in two variants, **Snapper-PCI-24** for RGB colour or monochrome video, and **Snapper-PCI-8** for monochrome only. Each channel is digitized via an 8 bit ADC, processed through an 8-bit programmable LUT (Look-Up Table), and then stored in on-board frame memory. Four software selectable inputs allow 4 RGB cameras or 12 mono cameras to be connected to a **Snapper-PCI-24** (or 4 mono cameras to a **Snapper-PCI-8**). A custom FPGA (field programmable gate array) then performs optional sub-sampling and region of interest generation for maximum flexibility and readout speed. The on-board frame buffer consists of two banks, each capable of holding 256K pixels. The frame memory architecture allows de-interlacing on readout. A programmable PLL (phase locked loop) and sync generator combined with the custom FPGA provides versatile sync and clock options for both input and output. An on-board hardware Data Mapper provides mapping and packing functions for the conversion of data, if required, to pixel formats suitable for immediate display.

The Software Developer's Kit (SDK), available as a separate item, allows rapid system development and integration. It provides comprehensive example applications and optimised libraries, and is available for a variety of operating systems including Windows 3.1x/95/98/NT, MacOS 7/8, MS-DOS, Solaris 2, LynxOS and VxWorks. As well as functions that control the hardware, the libraries include general purpose functions for the manipulation and display of images. A separate datasheet describes the SDK in detail.

## CAMERA INTERFACE SPECIFICATION

| Video Input:   | Each of the three ADCs has a four to one input multiplexer allowing each video channel to independently select one of four sources. Each video source is 75 Ohm terminated. The selection of any one of these video sources is under software control. On the <i>Snapper-PCI-24</i> this allows one of four RGB sources or three of twelve monochrome sources to be selected under software control. These three multiplexers have individual control, so if required the red input of channel 1 can be digitized at the same time as the green input of channel 3 and the blue input of channel 4. For the <i>Snapper-PCI-8</i> a maximum of four monochrome cameras can be supported. Video inputs are DC-restored to a programmable level. On the YCbCr version the RGB inputs can be redefined as YCbCr inputs, with the Cb and Cr inputs DC-restored to mid-level.                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Sampling:      | By default CCIR video signals (European) are sampled at 14.75MHz and EIA video signals (USA and Japan) at 12.27MHz, resulting in square pixel sampling for both standards. These sampling frequencies are fully programmable under software control, which can be useful for zero aliasing with the internal pixel clock for CCD cameras. The video standard can be auto-sensed. Images are digitized in real-time - i.e. 40ms for full frame CCIR and 33ms for EIA. Maximum sampling rate is 20MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Digital Video: | As default standard RGB or monochrome video signals are digitized to 24 bits (8 bits for each of red, green and blue) with black level at 0 and peak white at 255. The control of black and white level can be fully adjusted under software control. In the software library an AGC function is provided to set the levels to the above default one or several others including CCIR 601 quantization levels. On the YCbCr version, the default levels are 16 to 235 for luminance and 44 to 212 for chrominance (75% colour bars). These quantization levels conform to CCIR Recommendation 601-2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| LUTs:          | The output of each ADC drives a 256 by 8 look up table (LUT). This allows functions such as gamma correction, brightness, contrast, and thresholding to be performed in real time in hardware. For the <i>Snapper-PCI-24</i> the three LUTs can be accessed individually, or all three can be written in parallel for speed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Resolution:    | CCIR video images are digitized to a resolution of 768 x 576 and EIA (RS-170) video images to 640 x 480. These resolutions represent the full active picture area of the video signal. Non-standard cameras, such as line scan cameras can also be digitized in real-time at any resolution provided one frame or (one line) can fit into the frame store.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Sync:          | The sync source can be selected from one of the following:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                | <ul> <li>Any one of the video inputs (regardless of which of the inputs is being digitized).</li> <li>A separate 75 Ohm composite sync input CSYNC (which will accept negative going black level sync, or negative TTL level into 75 Ohms, or video including composite video).</li> <li>Separate horizontal sync and vertical sync inputs <i>HSYNC</i> and <i>VSYNC</i>. These are jumper selectable as either TTL or RS-422 (differential) levels. These inputs are individually programmable as negative or positive going.</li> <li>The on-board programmable sync generator.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                | The sync generator is fully programmable, with full register control of pulse widths and positions, interlaced / non-interlaced mode, and the presence / absence of double serration pulses. To ensure correct frequencies are generated the module is fitted with two crystal oscillators - one at 29.50MHz for CCIR use and one at 14.31818MHz for EIA use.<br>If <i>CSYNC</i> , <i>HSYNC</i> or <i>VSYNC</i> are not being used as inputs they can be individually driven as outputs. The output is in the same format as the corresponding input; i.e. <i>CSYNC</i> is black level (0.3V) into 75 Ohms, and <i>HSYNC</i> and <i>VSYNC</i> are either TTL or RS-422. <i>HSYNC</i> and <i>VSYNC</i> are individually programmable as negative or positive going. The <i>HSYNC</i> output can also be driven out as <i>CSYNC</i> with either TTL or RS-422 levels.<br>Note: Selection between TTL and RS-422 on <i>HSYNC</i> and <i>VSYNC</i> is achieved with jumpers. All other modes are controllable by software. <i>HSYNC</i> and <i>VSYNC</i> can be supplied to special order with 75 Ohm terminators fitted for use with sync sources which provide TTL levels into 75 Ohms, in which case the corresponding TTL outputs cannot be used. |  |

| Clock:         | The selected sync source drives the programmable phase locked loop (PLL), which normally provides the module's pixel clock. The PLL uses the latest monolithic frequency synthesizer technology, and allows control of pixels per line, phase detector gain, oscillator (VCO) gain, fast or slow loop filters, and a choice of four phases of clock (0°, 90°, 180° or 270°). The slow loop filter allows lock to poor sources such as video recorders. The PLL jitter is typically $\pm$ 3ns, worst case $\pm$ 7ns. Note that to achieve this performance a stable sync source, such as obtained using the separate <i>HSYNC</i> and <i>VSYNC</i> inputs, must be used. If a relatively poor sync source is used, such as composite video, typical jitter figures are around $\pm$ 7ns to $\pm$ 20ns. As an alternative to the PLL, the module's pixel clock can be provided by a pixel clock input 'PCLK'.                                                                                                                                                                                                                                                                                                                                       |  |

| During of Information                                                                                                                                                  | This is jumper selectable as either TTL or RS-422 (differential), and either the positive or negative edge can be selected as the active edge. If PCLK is not being used as an input it can be driven as an output, with either the positive or negative edge selected as the active edge. The output is in the same format as the input; i.e. either TTL or RS-422. PCLK can be supplied to special order with a 75 Ohm terminator fitted for use with clock sources which provide TTL levels into 75 Ohms, in which case the corresponding TTL output cannot be used. When PCLK is used, <i>HSYNC</i> and <i>VSYNC</i> inputs can function as line and frame enables. Note: Selection between TTL and RS-422 on PCLK is achieved with jumpers. All other modes are controllable by software                                                                                                                                               |                                                                                                                                                                           |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Region of Interest:                                                                                                                                                    | A region of interest (ROI) for acquisition and readout is software programmable. The horizontal start<br>and length are controllable to a resolution of 8 pixels and the vertical start and length are<br>controllable to a resolution of 2 lines. (The vertical start position must be less than 254 lines down<br>the field.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                           |  |

| Sub-sampling:                                                                                                                                                          | <ul><li>Sub-sampling can be performed in hardware and is software programmable. Sub-sampling can be by two or by four:</li><li>x2: Every 2nd pixel in the horizontal direction and only the first field of each frame.</li><li>x4: Every 4th pixel in the horizontal direction and every second line of the first field of each frame.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                           |  |

| Frame Store:                                                                                                                                                           | The video frame store consists of either 1 or 1.5 Mbytes of RAM configured as FIFO memory. The memory is arranged as two banks of 256K pixels - one bank for each video field. The two banks are accessed independently such that one field of data can be stored in the first memory bank whilst the previous field is read from the second. This allows data to be acquired at full video rates without missing fields. Alternatively the hardware can de-interlace captured video images on readout by switching banks on a line by line basis. (This de-interlacing method is hidden to the user in the software library). Colour data is stored as full 24 bits. 8 bit Grayscale data is pre-packed to 16 bits in the Frame Store so that 2 data pixels can be read in a single PCI clock, thus doubling the read out rate. This data can be mapped to other pixel formats using the Data Mapper, (see the PCI Bus Interface section). |                                                                                                                                                                           |  |

| Trigger:                                                                                                                                                               | A separate TTL / RS-422 trigger input 'TRIG' is provided for synchronization to external events - for<br>example to synchronize to a strobed flash gun. The polarity of the trigger input is software<br>programmable. Asynchronous reset cameras are fully supported in this mode.<br>If TRIG is not being used as an input it can be driven as an output under software control. The<br>output is in the same format as the input; i.e. either TTL or RS-422. TRIG can be supplied to special<br>order with a 75 Ohm terminator fitted for use with trigger sources which provide TTL levels into 75<br>Ohms, in which case the corresponding TTL output cannot be used.<br>Note: Selection between TTL and RS-422 is achieved with jumpers. All other modes are<br>controllable by software.                                                                                                                                             |                                                                                                                                                                           |  |

| Controls:                                                                                                                                                              | Brightness, contrast and DC restoration level are performed in hardware under software control.<br>These controls adjust the digitization levels for black level, white level and clamp level of the video<br>signal. For example, this level of control allows a small range of the input video to be digitized to<br>the maximum of 256 levels per ADC to provide contrast enhancement.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                           |  |

| Interrupts:                                                                                                                                                            | An interrupt signal is available and can be configured via software to interrupt on various events.<br>Consult the "Snapper-24 Library – Programmer's Manual" for more details. Polled operation is also<br>supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                           |  |

| +12V Out:                                                                                                                                                              | The raw +12V from the host machine power supply is output to provide power for the camera, if required. The output is protected by a resetable fuse, and is capable of sourcing 400mA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                           |  |

| Connectors:                                                                                                                                                            | A BNC connects to Red Input 1 on the Snapper and a 25 way D type socket connects additional signals to the <b>Snapper-PCI-8/24</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                           |  |

| Snapper-PCI-8:                                                                                                                                                         | <ul> <li>Snapper-PCI-8 is functionally identical to Snapper-PCI-24 with the following exceptions:</li> <li>Snapper-PCI-8 only has the Red channel ADC, and LUT fitted.</li> <li>Snapper-PCI-8 only has 1Mbyte of memory fitted, rather than 1.5MBytes</li> <li>Snapper-PCI-8 has the Clamp Voltage level fixed at 0.17V, rather than being software</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                           |  |

| USA<br>Active Silicon, Inc<br>479 Jumpers Hole Road, Suite 301,<br>Severna Park, MD 21146, USA<br>Tel +1 410 696 7642<br>Fax +1 410 696 7643<br>info@activesilicon.com |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Europe<br>Active Silicon Limited<br>Pinewood Mews, Bond Close, Iver<br>Bucks, SL0 ONA, UK<br>Tel +44 (0) 1753 650600<br>Fax +44 (0) 1753 651661<br>info@activesilicon.com |  |

All trademarks referred to in this datasheet are the property of their respective owners

prior to PCI bus transfer).

Data Rates:Bus master DMA supports 132 Mbytes/sec data transfer rate. The PCI data is generated by the<br/>Data Mapper reading from the Frame Buffer memory. For 24 bit RGB data, 1 pixel is transferred<br/>on each PCI clock, whereas for grayscale data, 4 pixels are transferred on alternate PCI clocks.

Address Range andAutomatically mapped to I/O space. Board requires 64 bytes of address space.Interrupts:Interrupts automatically selected by host operating system.

## PHYSICAL AND ENVIRONMENTAL DETAILS

| PCB: 149mm by 74mm. With connector (overall): 156mm by 74mm.                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| 104g.                                                                                                                                       |

| 10mm.                                                                                                                                       |

| P1386 Draft 2.0, 4th April 1995 and P1386.1 Draft 2.0, April 1995.                                                                          |

| +5V @ 1.9 Amps, +12V @ 20mA, -12V @ 15mA.                                                                                                   |

| $-15^{\circ}$ C to $+70^{\circ}$ C.                                                                                                         |

| $0^{\circ}$ C to $+55^{\circ}$ C.                                                                                                           |

| 10% to 90% non-condensing (operating and storage).                                                                                          |

| <b>C C</b> mark for compliance with EN 55022:1994 (class B) and EN 50082-1:1992 in accordance with EU directive 89/336/EEC.<br>FCC Class A. |

|                                                                                                                                             |

Full mechanical drawings are available on request.

## **ORDERING INFORMATION**

| PART NUMBER                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                         |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SNP-PCI-8<br>SNP-PCI-24      | <i>Snapper-PCI-8</i> monochrome frame capture board, or <i>Snapper-PCI-24</i> RGB frame capture board.                                                                                                                                                                                                                                              |  |

| CBL-25D-SNP<br>CBL-25D-SNP-8 | <b>Snapper-PCI-8/24</b> cable assembly. Both cables contain a trigger input/output and an analogue sync input/output. The CBL-25D-SNP also contains a single set of RGB inputs whereas the CBL-25D-SNP-8 contains four monochrome inputs. Other custom cables can be made to order. Please contact Active Silicon for more information.             |  |

| -                            | Software Developer's Kit.<br>For a full list of all supported operating systems, support contracts and other options,<br>please refer to the SDK datasheet, or contact Active Silicon directly. Currently<br>supported operating systems include Windows NT, Windows 95, Windows 98,<br>Windows 3.1x, MS-DOS, Solaris 2, VxWorks, LynxOS and MacOS. |  |

#### **ORDERING NOTES**

• Please contact Active Silicon for latest information on other Snappers, Bus Interface Boards, and supported OS.

#### **Connector Pinout**

A 25 way D type socket connects signals into the module.

| Pin Number | Snapper-PCI-24 |

|------------|----------------|

| 1          | GND            |

| 2          | Green 1        |

| 3          | Red 2          |

| 4          | Blue 2         |

| 5          | Green 3        |

| 6          | Red 4          |

| 7          | Blue 4         |

| 8          | +12V out       |

| 9          | Trigger -      |

| 10         | VSYNC -        |

| 11         | HSYNC -        |

| 12         | Pixel Clock -  |

| 13         | GND            |

| 14         | Red 1          |

| 15         | Blue 1         |

| 16         | Green 2        |

| 17         | Red 3          |

| 18         | Blue 3         |

| 19         | Green 4        |

| 20         | CSYNC          |

| 21         | Trigger +      |

| 22         | VSYNC +        |

| 23         | HSYNC +        |

| 24         | Pixel Clock +  |

| 25         | N/C            |

#### NOTES:

- 1. The signal names in *bold italics* are available on the standard cable, (Part number CBL-25D-SNP).

- 2. Signals labelled as *Sig*+ and *Sig* are the two halves of the RS-422 signals and must be connected to twisted pair cabling.

- 3. When using the TTL level trigger, connect the input to *TRIGGER*+.

THIS PAGE IS INTENTIONALLY BLANK